Laporan akhir 2 M1

[menuju akhir]

Gerbang OR adalah gerbang logika yang menggunakan operasi penjumlahan. Nilai output bernilai 0 hanya pada jika nilai semua input bernilai 0. Bila dilihat dari rangkaian dasarnya maka didapat tabel kebenaran seperti di atas. Pada gerbang logika OR ini bisa dikatakan bahwa jika salah satu atau lebih input bernilai 1 maka output akan bernilai 1.

c. Gerbang Exclusive OR (X-OR)

X-OR merupakan gerbang OR yang bersifat exlusif, di mana jika hasil penjumlahan inputnya bernilai ganjil maka outputnya bernilai 1 dan jika hasil penjumlahan inputnya bernilai genap maka outputnya bernilai 0.

d.Logics State

Logic State dapat dijadikan sebagai input yang akan memberikan logika 1 dan logika 0. Atau Gerbang Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan input-input yang berupa bilangan biner (hanya terdapat 2 kode bilangan biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean sehingga dihasilkan sebuah sinyal output yang dapat digunakan untuk proses berikutnya

e.Logic ProbeLogic Probe dijadikan sebagai hasil keluaran atau output. Dimana akan menampilkan logika 0 atau logika 1

f. Switch SPDT

SPDT adalah singkatan dari Single Pole Double Throw. Sederhananya, switch ini memiliki satu input (pole) dan dua output (throw). Fungsinya seperti sebuah saklar yang bisa mengalihkan arus listrik dari satu jalur ke jalur lainnya.

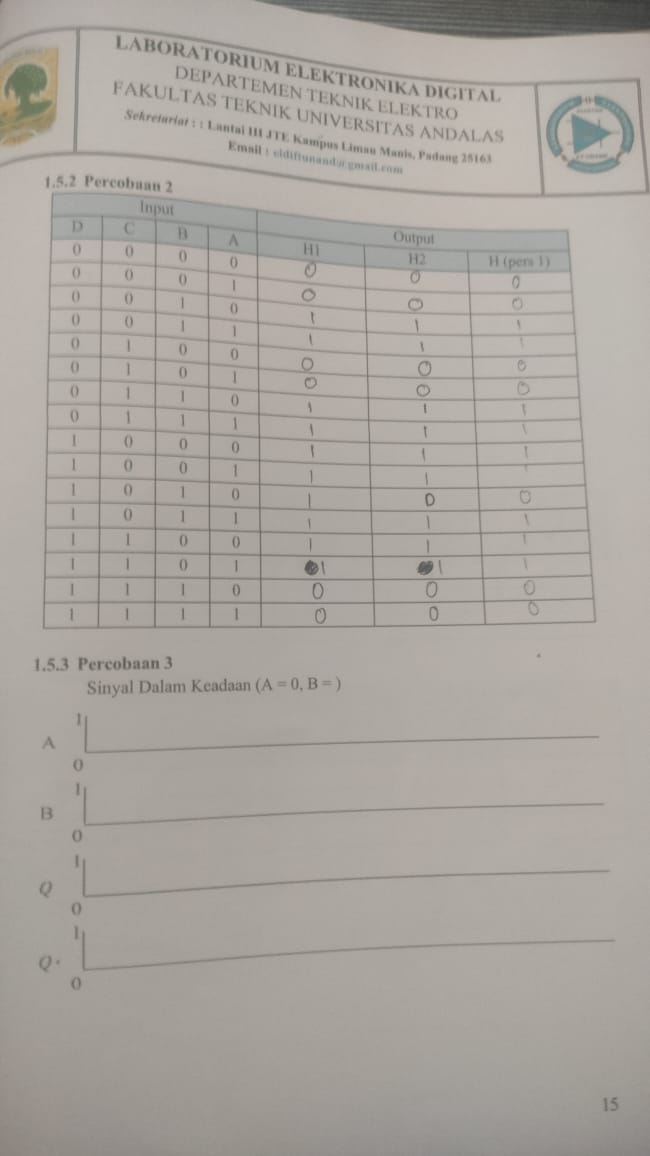

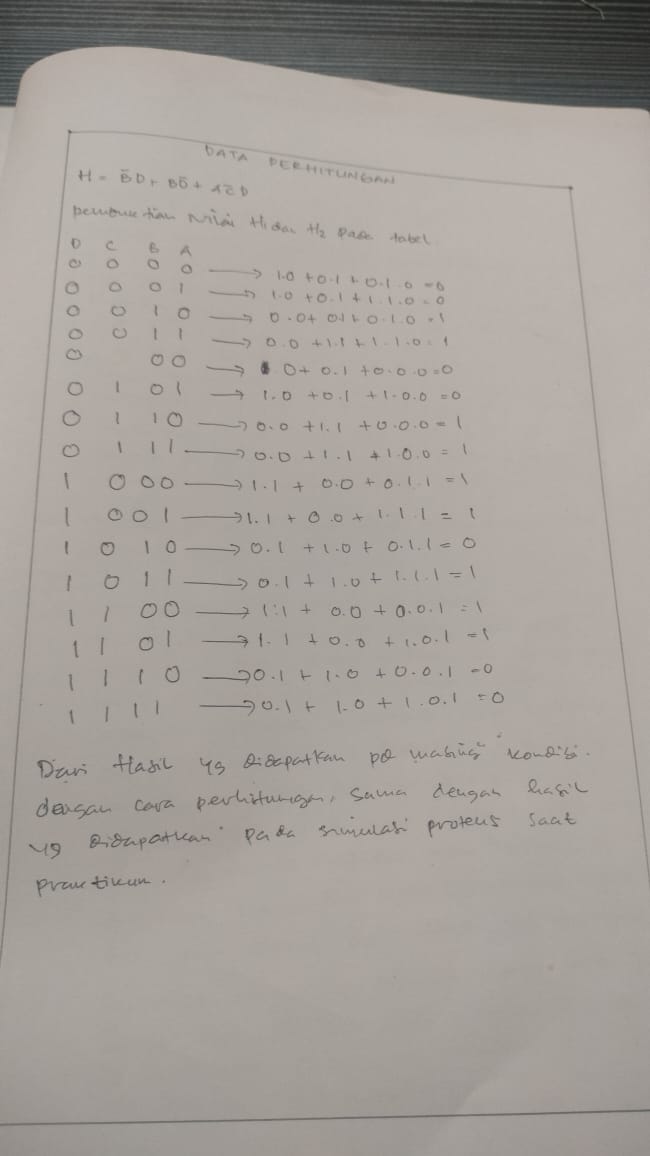

XOR Gate memiliki dua input yaitu B dan D. Output dari (XOR) adalah 1 jika B dan D berlogika berbeda (banyak input yang berlogika 1 berjumlah ganjil). Jika kedua inputnya sama (banyak input yang berlogika 1 berjumlah genap) maka outputnya akan berlogika 0. NOT Gate memiliki prinsip yaitu membalikkan nilai input C. Jika C adalah 0, maka outputnya 1, dan sebaliknya. (AND Gate) memiliki tiga input yaitu A, output dari (inversi C), dan D. Output dari AND akan 1 hanya jika ketiga inputnya 1 (Perkalian). (OR Gate) memiliki dua input yaitu output dari AND dan XOR, jika salah satu atau kedua inputnya 1 maka outputnya juga satu dan jika kedua input nol maka outputnya nol (Penjumlahan).

Komentar

Posting Komentar