Laporan Akhir 1 M1

[menuju akhir]

Laporan Akhir 1

Modul 1

Modul 1

2. Alat dan Bahan[Kembali]

1. Alat

a.. Jumper

Gambar 1. Jumper

b.Panel DL 2203D

c.Panel DL 2203C

d.Panel DL 2203S

Gambar 2. Modul De Lorenzo

2. Bahan

1. Gerbang Not

Gerbang NOT sering juga disebut sebagai rangkaian inventer (pembalik). Tugas rangkaian NOT (pembalik) ialah memberikan suatu keluaran yang tidak sama dengan masukan.

2. Gerbang AND

Gerbang AND merupakan salah satu gerbang logika dasar yang memiliki prinsip kerja perkalian. Nilai output akan berlogika 1 jika semua nilai input logika 1, dan jika salah satu atau lebih input ada yang berlogika 0 maka output akan berlogika 0.

3. Gerbang OR

Pada gerbang logika OR ini bisa dikatakan bahwa jika salah satu atau lebih input logika 1 maka output akan berlogika 1 . Nilai output logika 0 hanya pada jika nilai semua input berlogika 0.

4. Gerbang XOR

XOR merupakan gerbang OR yang bersifat exlusif, jika input logika 1 berjumlah genap (0,2,4, dst), maka hasil output akan berlogika 0, dan jika logika 1 berjumlah ganjil (1,3,5,dst), maka hasil output berlogika 1.

5. Gerbang NAND

Gerbang NAND adalah gerbang AND yang keluarannya disambungkan ke inverter. Nilai output akan berlogika1 jika salah satu atau lebih nilai input adalah berlogika 1, dan output akan berlogika 0 jika semua input berlogika 1.

6. Gerbang NOR

Gerbang NOR adalah gerbang OR yang disambung ke inverter. Gerbang NOR akan menghasilkan keluaran logika 0 jika salah satu dari masukkan (input) bernilai logika 1 dan jika ingin mendapatkan keluaran logika 1, maka semua masukan (input) harus bernilai logika 0.. Atau dapat menngunakan prinsip pernjumlahan, kemudian di NOT kan.

7. Gerbang XNOR

Gerbang XNOR adalah gerbang XOR yang diinverterkan. Jika input logika 1 berjumlah genap (0,2,4,dst), maka hasil output berlogika 1, dan jika input logika 1-nya berjumlah ganjil (1,3,5,dst) maka hasil output berlogika 0.

8. Logics State

Logic State dapat dijadikan sebagai input yang akan memberikan logika 1 dan logika 0. Atau Gerbang Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan input-input yang berupa bilangan biner (hanya terdapat 2 kode bilangan biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean sehingga dihasilkan sebuah sinyal output yang dapat digunakan untuk proses berikutnya

3. Rangkaian[Kembali]

Gambar 13. Gambar Rangkaian Dari Modul

4. Prinsip Kerja[Kembali]

Berdasarkan gambar-gambar di atas, percobaaan dilakukan dengan berbagai komponen dasar yaitu input dengan logic state dan clock, gerbang logika seperti gerbang NOT, gerbang AND, gerbang OR, gerbang XOR, gerbang NAND, gerbang NOR, dan gerbang XNOR. Untuk output menggunakan Logic probe.

1. Input B1 dan B0

Adapun percobaan 1 tabel yang pertama memiliki prinsip kerja yaitu berawal saat inputan (B0 dan B1) mengalirkan arus dengan kombinasi logikanya masing-masing ke gerbang logika. Di gerbang NOT outputnya adalah invers dari B1. Di gerbang AND outputnya adalah 1 jika kedua input adalah 1 dan 0 jika salah satu atau kedua inputnya 0 (perkalian). Di gerbang OR outputnya adalah 1 jika salah satu atau kedua input adalah 1 dan akan 0 jika kedua inputnya satu (penjumlahan). Di XOR outputnya adalah 1 jika hanya satu input yang berlogika 1 (banyak input dengan logika 1 berjumlah ganjil) sedangkan outputnya akan 0 jika inputnya sama (banyak input dengan logika 1 berjumlah genap). Di Gerbang NAND outputnya adalah 1 jika salah satu atau kedua inputnya adalah 0 dan outputnya 0 jika kedua inputnya 1. Hal ini juga berarti bahwa NAND adalah bentuk inversi dari AND. Di Gerbang NOR outputnya adalah 0 jika salah satu atau kedua inputnya adalah 1 dan outputnya 1 jika kedua inputnya 0. Hal ini juga berarti bahwa NOR adalah bentuk inversi dari OR. Di XNOR outputnya adalah 0 jika hanya satu input yang berlogika 1 (banyak input dengan logika 1 berjumlah ganjil) sedangkan outputnya akan 1 jika inputnya sama (banyak input dengan logika 1 berjumlah genap). Hal ini juga berarti bahwa XNOR adalah bentuk inversi dari XOR. Masing-masing output dari gerbang logika akan diteruskan dan ditampilkan logic probe yang dilambangkan dengan H1 sampai H7.

2. Input B1 dan Clock

Percobaan 1 tabel kedua memiliki prinsip kerja yang sama dimana input B0 dan B1 mengalirkan arus berlogika ke masing-masing gerbang logika kemudian outputnya ditampilkan oleh logic probe yang dilambangkan dengan huruf H dengan urutan 1 sampai 7. Namun yang membedakan dalam kondisi ini adalah input B0 diganti dengan clock yang mana logikanya berubah seiring waktu sehingga saat gerbang logika menerima inputan clock dan kondisi input dari B1 maka akan menghasilkan output berupa grafik clock, inversi dari clock, stabil di logika 1 dan stabil di logika 0 sesuai dengan jurnal.

5. Video Percobaan[Kembali]

6. Analisis[Kembali]

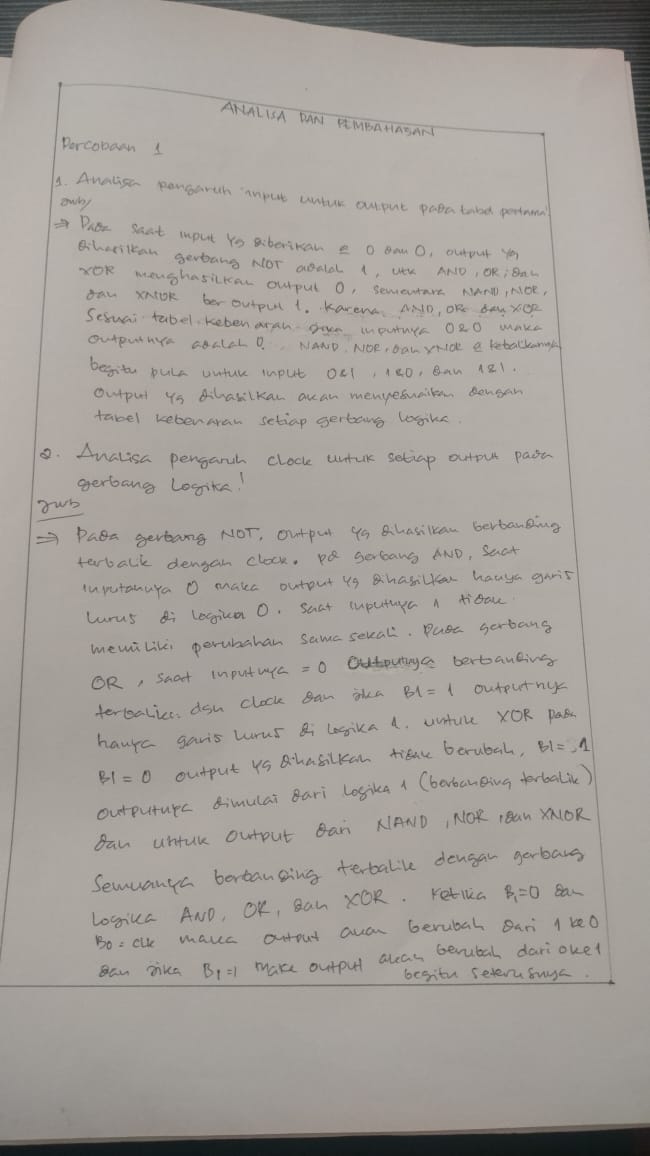

1. Analisa pengaruh input untuk output pada tabel pertama

2. Analisa pengaruh clock untuk setiap output pada gerbang logika

Komentar

Posting Komentar